MEMORIA ROM

1. Resumen

En este informe se encuentra toda la información acerca de la octava práctica de laboratorio de electrónica digital en donde se implemento una memoria con teclado matricial para el ingreso y almacenamiento de datos a partir de la PSoC.

2. Marco teórico

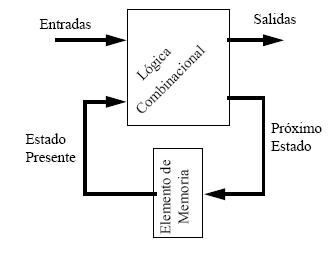

CIRCUITOS SECUENCIALES:

Los circuitos secuenciales trabajan bajo el dominio del tiempo principalmente, se marca una señal dada por un pulso de reloj que permite la funcionalidad del circuito dando la transición a un estado siguiente sin embargo, este tipo de circuitos trabaja con dispositivos de memoria que dan la utilidad de guardar los estados y trabajar a partir de ellos. La salida no solo depende de la entrada, sino de ademas de un estado anterior (historia de entradas).

Los circuitos secuenciales se clasifican en:

- sincronos

- asíncronos

En los sincronos el cambio de estado se da a partir de una constante natural marcado por los retardos según las configuraciones de cada montaje anexo.

En los asíncronos el cambio de estado se da a partir de una señal de tipo oscilatorio.

https://www.ecured.cu/images/8/87/Ejem.JPG

FLIP FLOP

El flip flop es el dispositivo básico utilizado como memoria para la programación de lógica secuencial.

http://hyperphysics.phy-astr.gsu.edu/hbasees/Electronic/ietron/jk.png

https://qph.fs.quoracdn.net/main-qimg-66ee472249fb37bef77c53c03db3b045

http://www.electronicsengineering.nbcaf

e.in/wp-content/uploads/2014/12/rs.png

http://i.stack.imgur.com/0u9q2.jpg

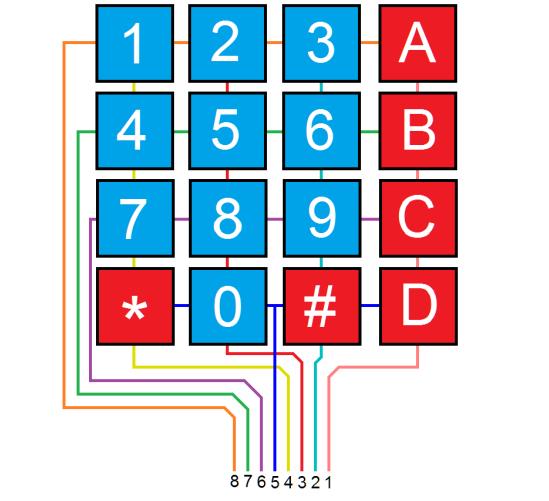

TECLADO MATRICIAL:

Un teclado matricial tiene muchas aplicaciones en la electrónica actual, como ensamblador de datos,ya que permite facilitar las señales de entrada de los datos. Esta compuesto por 4 filas y 4 columnas, cada tecla esta configurada para pertenecer por lo tanto a una fila y una columna, si la tecla no ha sido oprimida, la conexión entre fila y columna esta abierta, por o cual no se transmiten datos, solo cuando alguna tecla es oprimida o pulsada se genera la señal de entrada de datos al sistema al cual este configurado.

https://www.prometec.net/teclados-matriciales/

3. DESARROLLO PRÁCTICO

Para la implementación de la memoria ROM a base de componentes en PSoc de memorias de 1 bit, como se necesitaban memorias de 4 bits, se encapsularon 4 de bit para obtenerlas, cada memoria guarda números diferentes asignados a los valores de teclado matricial, para reconocer su lectura.

Imagen 2. Memoria 4 bits

Las salidas del decodificador de teclado matricial entran a la ROM para el proceso de lectura y almacenamiento de datos, las salidas de la ROM van al componente del integrado DM74181 para convertir el numero de binario a BCD, por ultimo se conectan estas salidas a las entradas de el decodificador de 7 segmentos, para hacer como en las practicas anteriores la visualización dinámica.

El uso de memorias es fundamental para el desarrollo de circuitos lógicos secuenciales, ya que nos permiten el cambio de estado y el almacenamiento practico de los diferentes datos que se están utilizando.

Para la parte que comprende la visualización dinámica se realizo el siguiente procedimiento:

Primero se creo un componente que permite la conversión de binario a BCD, el integrado DM74185, el cual se creo a partir de la herramienta de PSoC llamada LUT, que nos permitió crear el componente a partir de la tabla de verdad del mismo. De esta manea se creo un lut para cada bit del numero, se conectaron y se encapsularon en un único componente:

Para recibir y elegir adecuadamente el numero después de la conversión de binario a BCD se creo un mux 16:4 a partir de mux de 2:1 encapsulados en un solo componente, el mux tiene dos selectores coordinados por un clock a 1KHz que por medio de un contador de dos bits, permitió mandar las señales binarias para utilizar o activar los displays 7 segmentos (C.U; C.D; C.C; C.M):

Por ultimo las salidas del mux 16:4 van conectadas a las entradas de un decodificador BCD que codifica las entradas de 1 a 9 en binario a base de 4 bits (entradas) y las salidas a,b,c,d,f y g que son los nombres de los segmentos el display. Para crear este decodificador fue necesario sacar la tabla de verdad para cada salda de cada segmento e implemetarse en un LUT, las cuales son:

Al realizar adecuadamente las conexiones entre componentes, obtuvimos el siguiente montaje esquemático para el proyecto:

Imagen 8. Memoria

4. CONCLUSIONES

Comentarios

Publicar un comentario